DATA SHEET

# M8030A Multi-Channel BERT

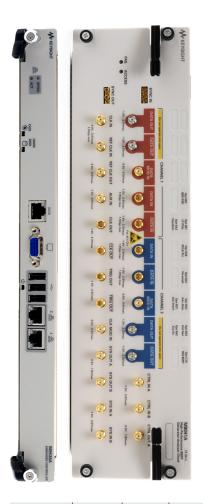

The Keysight Technologies, Inc. M8030A multi-channel BERT provides a solution for J-BERT applications that require more than four channels. It supports up to 10 pattern generators and up to 10 analyzer channels for cases where multi-channel test applications, like PCIe<sup>®</sup>, passive optical network (PON) or ATE like applications are a must.

Due to the increasing complexity of devices and higher data rates, testing is more critical and complex. While single-lane testing might be sufficient at lower speeds, higher data rates increase the probability of crosstalk problems, making the use of multi-lane testing with different aggressor and victim signals more important. When multi-channel measurements are required in order to speed up throughput or test under real application conditions, the M8030A is the perfect tool.

#### M8020A modules

The M8030A multi-channel BERT is 100 percent compatible with available J-BERT M8020A modules. Its ability to support the M8041A and the M8051A J-BERT modules protects your existing module investment. The AXIe embedded controller is also supported and can be easily used along with M8041A/51A J-BERT modules to create an integrated and highly compact test environment. For more details on available configurations, please see the Configuration Guide section in this data sheet.

### **Applications**

The M8030A multi-channel BERT is designed for R&D and test engineers characterizing and verifing compliance of chips, devices, boards, and systems with multiple I/O ports up to 16 Gb/s, which are used in various industry segments dealing with computer devices, communication equipment, and others. Typical applications include:

- PCIe multi-channel tests

- PON ATE test (when a low number of channels is sufficient)

- 40GBASE and 100GBASE ports using 4 and 10 Gb/s ports

#### **Features**

- Data rates up to 8.5 Gb/s and 16 Gb/s

- Up to 10 BERT pattern generator and analyzer channels in a 14-slot AXIe chassis

- Integrated and calibrated jitter injection: RJ, PJ1, PJ2, SJ, BUJ, sinusoidal level interference (common-mode and differential-mode), SSC (triangular and arbitrary, residual) and clock/2

- Clock synchronization between all modules

- 8 tap de-emphasis, positive and negative

- Integrated jitter, de-emphasis and adjustable ISI, for each channel individually

- Interactive link training for PCI Express®

- Individually adjustable generator channel delay and pattern sequence

- Built-in clock recovery and equalization

- All options and modules are upgradeable

#### Benefits

- Increases test efficiency with higher throughput when testing multiple channels simultaneously

- Protects and leverages your investment in M8041A and M8051A modules by using them in J-BERT M8020A and M8030A BERT configurations

- Keeps-up with your test needs by enabling the addition of modules and required options as needed

- Ease of use by applying the same M8070A software for both, M8030A multi-channel BERT and J-BERT M8020A

- Minimizes the number of signal degrading reflections resulting from high-speed switches in your test setup

## M8000 Series of BER Test Solutions

Simplified, time-efficient testing is essential when you are developing next-generation computer, consumer, or communication devices.

The Keysight M8000 Series is a highly integrated BER test solution for physical layer characterization, validation, and compliance testing.

With support for a wide range of data rates and standards, the M8000 Series provides accurate, reliable results that accelerate your insight into the performance margins of high-speed digital devices.

### M8000 Series of BER test solutions Highly integrated and scalable for simplified, time efficient testing

- Multi-channel applications

- Interactive link training

- Analyzer equalization and clock recovery

- In situ calibration, de-embedding

- Expandable to higher data rates up to 32 Gb/s

- Higher integration: 16G BERT with 1-4 channels, jitter, de-emphasis

$\label{thm:prop:prop:section} Figure~1.~The~M8000~Series~BER~test~solution~is~highly~integrated~and~scalable~to~address~the~challenges~of~the~next~generation~of~high-speed~digital~receiver~test.$

## M8030A Multi-Channel PCIe Receiver Test Application

The M8030A multi-channel BERT is a highly integrated receiver test system that can be configured for testing of up to 10 lanes, each with up to 16.2 Gb/s. Each pattern generator of the M8041A or M8051A module can be equipped with built-in impairments like timing jitter, amplitude interference, and channel emulation. It is the ideal solution for characterizing chipsets interfaces with multiple lanes or multiple ports.

Figure 2 shows an example of a characterization setup of a test chip with a PCI Express interface operating with a common reference clock. Each of the lanes can be stimulated and analyzed simultaneously. To emulate a real world scenario as closely as possible, each of the receiver ports can be stressed with independent jitter frequency and amplitude, allowing edges of neighboring channels to move throughout the victim's eye. Measurements like jitter tolerance characterization can be executed on each lane independently.

Compared to serial BERT setups, the M8030A increases the test throughput.

TX 0 TX 1 TX 2 **TX** 3 PCIe test TX 4 TX 6 RX 6 Ref Clk TX 7

Figure 2. PCle x8 receiver test setup for ASIC test.

The PCI test solution offers:

- Up to eight PCI Express lanes that can be tested simultaneously

- The ability to equip each PG with full stress capabilities, including channel loss emulation data rates 5 Gb/s and higher

- Fully simulated crosstalk effects in each pattern generator by modulating with low frequency SJ

- Setup recommendations for test chips, which can be forced into a test mode

## M8030A PON Test Application

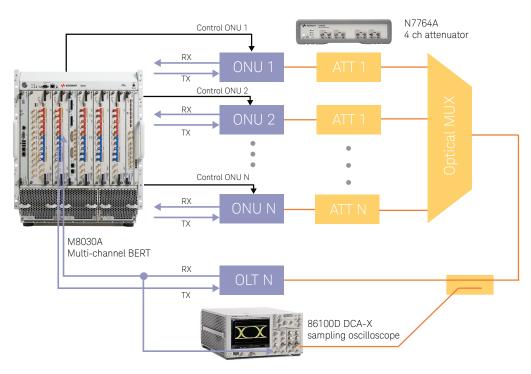

Passive optical networks (PON) are based on time division multiple access (TDMA) as used by GPON, BPON, EPON, and the emerging NG-PON. In this system, the most critical sub-module is the receiver RX of the optical line terminal (OLT) in the central office, which has to address the upstream signal bursts arriving from the optical network units (ONU) as shown in Figure 3. The timing of the bursted pattern on each channel, the control of the number of preamble bits, and timing of the required control signals are challenging.

Figure 3 shows a test setup consisting of an M8030A with M8041A and M8051A modules, Keysight's Lightwave Measurement System (LMS) 8163B/8164B, and a digital communication analyzer (DCA-X) 81600D emulating the important portions of a PON. The exact timing capability for the two data bursts and the related laser control signals is essential for standard-compliant testing and characterization of the OLT's receiver. The pattern sequencer allows the set-up and generation of the burst-packages with the desired content.

Figure 3. The M8000 Series BER test solution is highly integrated and scalable to address the test challenges of the next generation of high-speed digital receiver test.

#### The M8030A provides:

- One to 10 synchronized pattern generator channels; analyzer configurable as one channel

- Powerful pattern sequencer that allows the setup of data bursts and control signals, and options to use "CTRL OUT" or data outputs for control signals, depending on the timing resolution required

- Masking of the analyzer's expected pattern to measure the BER only on payload

- Clock recovery to deal with bursted data

- Scripting interface, IronPython, to control other instruments in the test setup

- DUT control interface to read out error counters of the DUT

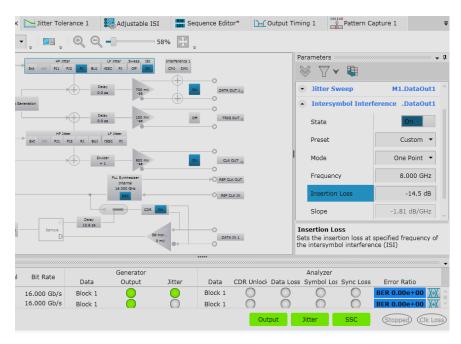

## M8070A System Software for M8000 Series of BER Test Solutions

The M8030A is controlled from the Keysight M8070A system software, the same software platform used to control the J-BERT M8020A high performance BERT. This saves time and money since it eliminates the need to learn a new multi-channel test environment.

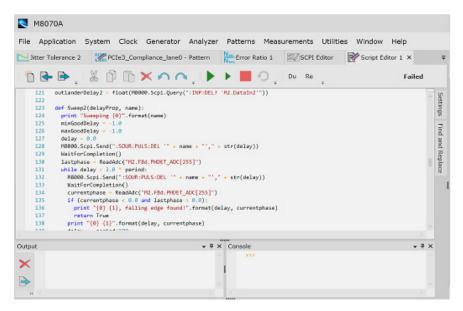

The M8070A software platform can be extended with software plug-in modules like the MIPI® M8085A. In addition, it is possible to add your own software to control an external DUT. For example, you may require to read BER from an external DUT through your software. This control interface needs to be written in broadly known IronPhyton. The M8070A provides full programming environment with interpreter, library and programming examples for IronPhyton.

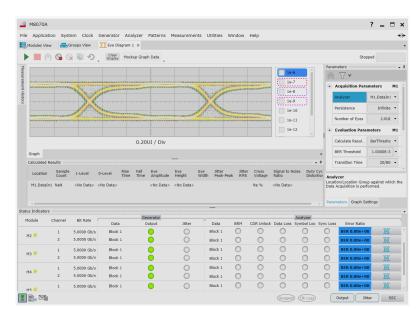

Figure 4. The M8070A graphical user interface showing the system view.

Figure 5. The IDE for Ironphyton DUT control interface.

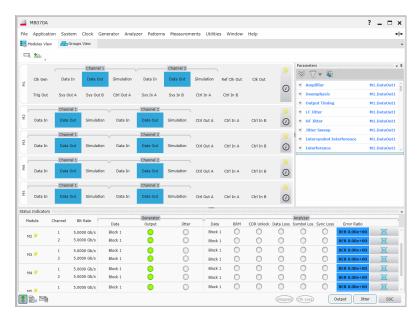

## M8070A System Software for M8000 Series of BER Test Solutions (Continued)

The M8070A system software's module view provides an easy to understand overview of the module and channel configuration. As shown in Figure 6, the system view gives an immediate overview of the status of each channel. Using module view, parameters related to connectors can be modified according to the test application. An overview screen provides a quick summary of the status of the outputs, locking of the error detectors, and BER.

Figure 6. M8030A module view configured with 1x M8041A and 4x M8051A.

In the analyzer view, various types of result analysis are available. In Figure 7 the color-coded eye diagram measurement is shown. In addition to this, eye-contour measurements, output timing, output level, jitter tolerance measurements, and bit error ratio measurements are provided for each channel individually, for up to 10 channels.

Figure 7. M8030A configured with 10 channels showing a color-coded eye diagram of one analyzer channel.

# Specifications for M8030A

| Sys Clock Input (from master M8041A module)         |                                                  |

|-----------------------------------------------------|--------------------------------------------------|

| Connector and cable type                            | Proprietary multi-coax (M8041-61614)             |

| Sys Clock Output (to M8041A and M8051A modules)     |                                                  |

| Connector and cable type                            | Proprietary multi-coax (M8041-61614)             |

| Skew (Data out to Data out/Trigger out to Data out) |                                                  |

| Factory De-Skew accuracy                            | ± 80 ps (without system level calibration)       |

| Repeatability                                       | 5 ps (after changes of data rate or power cycle) |

| Delay resolution for skew calibration               | 100 fs                                           |

The M8030A multi-channel BERT uses the M8041A, M8051A and the M8192A modules. For more detail on M8030A modules, please refer to the following data sheets:

| Publication title                                            | Publication number |

|--------------------------------------------------------------|--------------------|

| J-BERT M8020A High-Performance BERT - Data Sheet Version 3.5 | 5991-3647EN        |

| M8192A Multi-Channel Synchronization Module - Data Sheet     | 5991-2863EN        |

| M9537A AXIe Embedded Controller - Data Sheet                 | 5992-1530EN        |

# Configuration and Ordering Information

The M8030A is a modular test solution that can be tailored to your specific needs, from two channels with one M8041A, to up to 10 channels. Two bundles are available, depending on if an embedded PC is required:

| Bundle       | Description                                                                                       |

|--------------|---------------------------------------------------------------------------------------------------|

| M8030A-BU1 1 | Includes an M9537A embedded controller, 14-slot AXIe chassis, and pre-installed software licenses |

| M8030A-BU2   | Requires an external PC, connected to the M9521A controller in the M8030A via PCIe                |

$<sup>1. \</sup>quad \text{When using many channels M8030A-BU1 is recommend to improve control speed}.$

# Configuration and Ordering Information

| Slot       | Slot      | Slot       | Slot   |

|------------|-----------|------------|--------|

| #1         | #2        | #3         | #4     |

| M9537A     | M8141A J  | -BERT Hig  | h-     |

| AXIe       | performar | nce BERT r | nodule |

| embedded   |           |            |        |

| controller |           |            |        |

| Slot      | Slot    |

|-----------|---------|

| #5        | #6      |

| M8151A J  | -BERT   |

| High-perf | ormance |

| BERT mod  | lule    |

|           |         |

|           |         |

| 3101   |

|--------|

| #7     |

| M9521A |

| AXIe   |

| System |

| Module |

|        |

| 3101      | 3101    |

|-----------|---------|

| #8        | #9      |

| M8151A J  | -BERT   |

| High-perf | ormance |

| BERT mod  | lule    |

|           |         |

| #10       | #11     |

|-----------|---------|

| M8151A J  | -BERT   |

| High-perf | ormance |

| BERT mod  | lule    |

|           |         |

| Slot      | Slot    |

|-----------|---------|

| #12       | #13     |

| M8151A J  | -BERT   |

| High-perf | ormance |

| BERT mod  | lule    |

|           |         |

| #14    |

|--------|

| M8192A |

| AXIe   |

| Clock  |

| Sync   |

| module |

Slot

| Slot number | Module configuration rules                                                                                 |

|-------------|------------------------------------------------------------------------------------------------------------|

| 1           | M8030A-BU1 AXIe embedded controller. For M8030A-BU2 this slot is empty and covered with filler front-plane |

| 2 to 4      | M8041A-xxx module, mandatory                                                                               |

| 5 to 6      | M8051A-xxx module, optional                                                                                |

| 7           | M9521A AXIe system module, always included in M8030A-BU1 or M8030A-BU2, must be in this slot               |

| 8 to 9      | M8051A-xxx module, optional                                                                                |

| 10 to 11    | M8051A-xxx module, optional                                                                                |

| 12 to 13    | M8051A-xxx module, optional                                                                                |

| 14          | M8192A AXIe clock sync module, multi-channel synchronization module, mandatory                             |

# Ordering Information

| Model                   | Description                                                                                                           |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------|

| M8030A                  | Multi-channel BERT                                                                                                    |

| M8030A-BU1              | Bundle consisting of one M9514A 14-slot AXIe chassis and one M9537A AXIe embedded PC controller with 16 GB RAM option |

| M8030A-BU2              | Bundle consisting of one M9514A 14-slot AXIe chassis                                                                  |

| M8041A                  |                                                                                                                       |

| M8041A-C08 <sup>1</sup> | BERT one channel, data rate up to 8.5 Gb/s                                                                            |

| M8041A-C16 <sup>1</sup> | BERT one channel, data rate up to 16 Gb/s                                                                             |

| M8041A-G08 <sup>1</sup> | Pattern generator one channel, data rate up to 8.5 Gb/s                                                               |

| M8041A-G16 <sup>1</sup> | Pattern generator one channel, data rate up to 16 Gb/s                                                                |

| M8051A                  |                                                                                                                       |

| M8051A-C08 <sup>1</sup> | BERT one channel, data rate up to 8.5 Gb/s                                                                            |

| M8051A-C16 <sup>1</sup> | BERT one channel, data rate up to 16 Gb/s                                                                             |

| M8051A-G08 <sup>1</sup> | Pattern generator one channel, data rate up to 8.5 Gb/s                                                               |

| M8051A-G16 <sup>1</sup> | Pattern generator one channel, data rate up to 16 Gb/s                                                                |

| M8070A                  |                                                                                                                       |

| M8070A-0NP              | System software for M8000 Series of BER test solutions, network/floating, perpetual license                           |

| M8070A-0TP              | System software for M8000 Series of BER test solutions, transportable, perpetual license                              |

| M8070A-1NP              | DUT control interface, network/floating, perpetual license                                                            |

| M8070A-1TP              | DUT control interface, transportable, perpetual license                                                               |

| M8192A                  |                                                                                                                       |

| M8192A                  | Synchronization module for M8190A or M8051A modules                                                                   |

<sup>1.</sup> For additional software licenses, see Keysight J-BERT M8020A - Data Sheet.

## **Related Products**

| Model      | Description                                                                              |

|------------|------------------------------------------------------------------------------------------|

| M8051A-802 | Clock crossover distribution cable for M8051A (M8041-61614)                              |

| N4910A     | Matched cable pair, 85 cm long, 2.4 mm (m f) to 2.4 mm (m f) for data outputs and inputs |

| Y1221A     | AXIe filler module single slot                                                           |

| Y1229A     | Rail kit for M9514A AXIe chassis                                                         |

| Y1234A     | Protective cover for M9514A AXIe chassis                                                 |

| Y1206A     | Keyboard and optical mouse                                                               |

# Step-by-Step Configuration Guide

The M8030A multi-channel BERT is scalable and consists of:

- BERT modules: M8041A and up to four M8051A modules

- M8192A clock synchronization module

- M8070A system software

- Infrastructure such as chassis and embedded controller

- Accessories

- Services

The following steps will guide you through configuring a turn-key M8030A multi-channel BERT.

| Option     | Description                                                                                                                                                                                                                |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Step 1     | Choose a 14-slot chassis and select the way you want to control the modules; usage without a chassis is not possible                                                                                                       |

| M8030A-BU1 | AXIe chassis, 14-slot with embedded AXIe controller. Software is pre-installed on embedded controller. This option is recommended when the setup is remotely controlled                                                    |

| M8030A-BU2 | AXIe chassis, 14-slot; does not include a PC. Customer requires an external PC. Recommended configuration if the user needs M8041A with several M8051A modules. External PC needs to be connected using the PCIe interface |

| M9048A     | PCIe desktop adapter: Gen2, x8, clock isolation is needed if option M8030A-BU2 is selected and highest download speed is required. Not needed if the USB interface is used                                                 |

| M9045B     | PCIe laptop adapter: Gen1, x1 is needed if Option M8030A-BU2 is selected and highest download speed is required                                                                                                            |

| Step 2     | Choose the 1st BERT module - basic configuration selection                                                                   |

|------------|------------------------------------------------------------------------------------------------------------------------------|

|            | M8041A 8.5/16 Gb/s generator analyzer clock, 3-slot AXIe module. One selection out of the following four options is required |

| M8041A-C08 | BERT, one channel, data rate up to 8.5 Gb/s                                                                                  |

| M8041A-C16 | BERT, one channel, data rate up to 16 Gb/s                                                                                   |

| M8041A-G08 | Pattern generator, one channel, data rate up to 8.5 Gb/s                                                                     |

| M8041A-G16 | Pattern generator, one channel, data rate up to 16 Gb/s                                                                      |

| Step 3     | Choose the 1st BERT module – optional selections M8041A 8.5/16 Gb/s generator analyzer clock, 3-slot AXIe module                |

|------------|---------------------------------------------------------------------------------------------------------------------------------|

| M8041A-0A2 | Second channel for analyzer, license, only valid if Option M8041A-C08 or M8041A-C16 is ordered                                  |

| M8041A-0A3 | Analyzer equalization, module-wide license, only valid if Option M8041A-C08 or M8041A-C16 is ordered                            |

| M8041A-0G2 | Second channel for pattern generator, license                                                                                   |

| M8041A-0G3 | Advanced jitter sources for receiver characterization, module-wide license                                                      |

| M8041A-0G4 | 8-tap de-emphasis, module-wide license                                                                                          |

| M8041A-0G5 | Adjustable Inter-symbol Interference (ISI), module-wide license                                                                 |

| M8041A-0G6 | Reference clock input with multiplying PLL, clock-group-wide license                                                            |

| M8041A-0G7 | Level interference sources for receiver characterization, module-wide license                                                   |

| M8041A-0S1 | Interactive link training for PCI Express, clock-group-wide license, requires Option 0G4 to allow de-emphasis negotiation. Only |

|            | valid if Option C08 or C16 is ordered                                                                                           |

| M8041A-0S2 | SER/FER analysis for coded and re-timed loop-back, clock-group-wide license. Only valid if Option C08 or C16 is ordered         |

| Option      | Description                                                                                         |

|-------------|-----------------------------------------------------------------------------------------------------|

| Step 4      | Choose the 2nd BERT module – basic selection                                                        |

|             |                                                                                                     |

|             | M8051A 8.5/16 Gb/s generator analyzer, 2-slot AXIe module; requires a M8041A module in slots 2 to 4 |

| M8051A-C08  | BERT, one channel, data rate up to 8.5 Gb/s                                                         |

| M8051A-C16  | BERT, one channel, data rate up to 16 Gb/s                                                          |

| M8051A-G08  |                                                                                                     |

| 100031A-000 | Pattern generator, one channel, data rate up to 8.5 Gb/s                                            |

| Step 5     | Choose the 2nd BERT module – optional selections M8051A 8.5/16 Gb/s generator analyzer, 2-slot AXIe module |

|------------|------------------------------------------------------------------------------------------------------------|

| M8051A-0A2 | Second channel for analyzer, license; only valid if Option M8051A-C08 or M8051A-C16 is ordered             |

| M8051A-0A3 | Analyzer equalization, module-wide license; only valid if Option M8051A-C08 or M8051A-C16 is ordered       |

| M8051A-0G2 | Second channel for pattern generator; license                                                              |

| M8051A-0G3 | Advanced jitter sources for receiver characterization, module-wide license                                 |

| M8051A-0G4 | 8-tap de-emphasis, module-wide license                                                                     |

| M8051A-0G5 | Adjustable inter-symbol interference ISI, module-wide license                                              |

| M8041A-0G7 | Level interference sources for receiver characterization, module-wide license                              |

|  | Step 6 | For 2nd, 3rd, and 4th M8051A modules, repeat Steps 4 and 5 |

|--|--------|------------------------------------------------------------|

|--|--------|------------------------------------------------------------|

| Step 7 | Choose M8192A clock synchronization module if not already available. This module is required for all combinations of M8041A and any number of M8151As |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | APPENDED FOR AND STORE AND                                                                                        |

| M8192A | M8192A multi-channel synchronization module for M8190A and M8030A multi-channel RERT                                                                  |

| Step 8     | Choose BER test system software; must select one of two options |

|------------|-----------------------------------------------------------------|

| M8070A-0TP | Transportable license for M8000 software                        |

| M8070A-ONP | Network license for M8000 software                              |

| Step 9     | Test automation software for PCIe, USB, SATA RX test is not a part of the M8030A multi-channel J-BERT structure. Order if needed |

|------------|----------------------------------------------------------------------------------------------------------------------------------|

| N5990A-010 | Required option                                                                                                                  |

| N5990A-101 | Support for PCI Express Gen1, Gen2, and Gen3 receiver tests for M8000                                                            |

| N5990A-102 | Support for USB 2.0 and 3.0 receiver tests for M8000 (USB 3.0 only)                                                              |

| N5990A-103 | Support for SATA 1.0, 2.0, and 3.0 RSG tests for M8000                                                                           |

| N5990A-301 | PCI Express 3.0 link training suite for M8000                                                                                    |

| N5990A-501 | PCI Express link equalization tests                                                                                              |

| N5990A-302 | USB 3.0 and 3.1 link training suite for M8020A                                                                                   |

| N5990A-303 | SATA link training suite for M8020A                                                                                              |

| N5990A-155 | DisplayPort receiver test for M8020A                                                                                             |

| N5990A-165 | MIPI M-PHY® receiver test for M8020A                                                                                             |

| N5990A-365 | MIPI M-PHY frame generator for M8020A                                                                                            |

| Option-No  | Description                                                                              |

|------------|------------------------------------------------------------------------------------------|

| Step 10    | Choose accessories                                                                       |

| N4910A     | Matched cable pair, 85 cm long, 2.4 mm (m f) to 2.4 mm (m f) for data outputs and inputs |

| M8051A-802 | Clock cross-over distribution cable for M8051A                                           |

| Y1221A     | AXIe filler module single slot                                                           |

| Y1229A     | Rail kit for M9514A AXIe chassis                                                         |

| Y1234A     | Protective cover for M9514A AXIe chassis                                                 |

| Y1206A     | Keyboard and optical mouse                                                               |

| Step 11     | Choose service plan                                             |

|-------------|-----------------------------------------------------------------|

| R1380-M80XX | Service for M8000 Series of BER test solutions                  |

| PS-S10      | Remote scheduled productivity assistance. Select 1 to 999 hours |

| PS-S20      | Startup assistance (one day)                                    |

| Step 12    | Upgrades for M8041A                                                                                           |

|------------|---------------------------------------------------------------------------------------------------------------|

| M8041A-U16 | Upgrade to 16 Gb/s data rate from M8041A-G08 and M8041A-C08, module-wide license                              |

| M8041A-UA2 | Upgrade of M8041A to second channel for analyzer, license                                                     |

| M8041A-UA3 | Upgrade of M8041A to analyzer equalization, module-wide license                                               |

| M8041A-UED | Upgrade to BERT from M8041A-G08 and M8041A-G16, module-wide license                                           |

| M8041A-UG2 | Upgrade of M8041A to second channel for pattern generator, license                                            |

| M8041A-UG3 | Upgrade of M8041A to advanced jitter sources for receiver characterization, module-wide license               |

| M8041A-UG4 | Upgrade of M8041A to multi-tap de-emphasis, module-wide license                                               |

| M8041A-UG5 | Upgrade of M8041A to adjustable inter-symbol interference (ISI) for all S/N, module-wide license <sup>1</sup> |

| M8041A-UG6 | Upgrade of M8041A to reference clock input with multiplying PLL, clock group-wide license                     |

| M8041A-UG7 | Upgrade of M8041A to advanced interference sources for receiver characterization, module-wide license         |

| M8041A-US1 | Upgrade of M8041A to interactive link training for PCI Express, clock group-wide license                      |

| M8041A-US2 | Upgrade of M8041A to SER/FER analysis for coded and re-timed loop-back, clock group-wide license              |

| Step 13    | Upgrades for M8051A                                                                                           |

|------------|---------------------------------------------------------------------------------------------------------------|

| M8051A-U16 | Upgrade to 16 Gb/s data rate from M8051A-G08 and M8051A-C08, module-wide license                              |

| M8051A-UA2 | Upgrade of M8051A to second channel for analyzer, license                                                     |

| M8051A-UA3 | Upgrade of M8051A to analyzer equalization, module-wide license                                               |

| M8051A-UED | Upgrade to BERT from M8051A-G08 and M8051A-G16, module-wide license                                           |

| M8051A-UG2 | Upgrade of M8051A to second channel for pattern generator, license                                            |

| M8051A-UG3 | Upgrade of M8051A to advanced jitter sources for receiver characterization, module-wide license               |

| M8051A-UG4 | Upgrade of M8051A to multi-tap de-emphasis, module-wide license                                               |

| M8051A-UG5 | Upgrade of M8051A to adjustable inter-symbol interference (ISI) for all S/N, module-wide license <sup>1</sup> |

| M8051A-UG7 | Upgrade of M8051A to advanced interference sources for receiver characterization, module-wide license         |

<sup>1.</sup> For serial numbers < DE55300500, this upgrade requires "return -to-factory".

## Default accessories included with shipment

| Option-No     | Description                                                                                                                 |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------|--|

| M8041A module | Eight 50 Ω terminations, commercial calibration report ("UK6"), certificate of calibration, and ESD protection kit          |  |

| M8051A module | Four 50 Ω terminations, clock synchronization cable (M8051A-802), commercial calibration report ("UK6"), and certificate of |  |

|               | calibration                                                                                                                 |  |

| M8030A-BU1    | M9514A AXIe chassis with embedded controller, USB cable, Getting Started Guide, AXIe filler panel, and power cord           |  |

| M8030A-BU2    | M9514A AXIe chassis, USB cable, Getting Started Guide, AXIe filler panel, and power cord                                    |  |

| M8070A        | CD-ROM with M8070A system software                                                                                          |  |

| Publication title                                                                                              | Publication number |

|----------------------------------------------------------------------------------------------------------------|--------------------|

| M8030A Multi-Channel BERT - Data Sheet                                                                         | 5992-1287EN        |

| M9514A and M9521A AXIe 14-Slot Chassis and AXIe System Module - Data Sheet                                     | 5991-3908EN        |

| Understand MIPI M-PHY Receiver Test Challenges and Solutions - Application Brief                               | 5991-3959EN        |

| How to Pass Receiver Test According to PCI Express® 3.0 CEM Specification with Add-In Cards and Motherboards - | 5990-9208EN        |

| Application Note                                                                                               |                    |

| Accurate Calibration of Receiver Stress Test Signals for PCI Express® rev. 3.0 - Application Note              | 5990-6599EN        |

| How to Test a MIPI M-PHY High-Speed Receiver - Challenges and Agilent Solutions - Application Note             | 5991-2848EN        |

| Master your next PCI Express® Test J-BERT M8020A High-Performance BERT - Application Brief                     | 5991-4190EN        |

| Master Your Next USB 3.x Designs with the J-BERT M8020A High-Performance BERT - Application Brief              | 5991-4357EN        |

| Characterizing and Verifying Compliance of 100 Gb Ethernet Components and Systems - Application Brief          | 5992-0019EN        |

# Learn more at: www.keysight.com

For more information on Keysight Technologies' products, applications or services, please contact your local Keysight office. The complete list is available at: www.keysight.com/find/contactus